BeagleBone + Botic + BBB �u���b�W��� DSD �l�C�e�B�u��

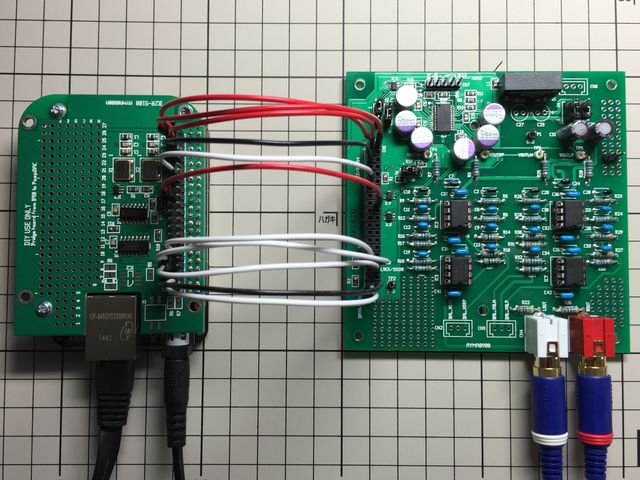

BeagleBone Black �� BBB �u���b�W��� B2R-5100 ���g���� I2S �C���^�[�t�F�[�X�Ńn�C���]�������Đ����邱�Ƃ��ł��܂����BRaspberry Pi �ł� 192kHz/24bit �� PCM �����܂łł��� BeagleBone Black �ł� 384kHz/32bit �� PCM �����ł̊m�F���ł��Ă��܂��B

Botic �� DSD �����̍Đ����\�ƂȂ��Ă��܂��̂Ŏ��̓l�C�e�B�u DSD �Đ��Ƀ`�������W���悤�Ǝv���܂��BBBB �u���b�W��� Botic �� DSD �C���^�[�t�F�[�X���T�|�[�g����悤�ɐv����Ă��܂��i���̂͂��j�̂ł��̊���g���čs���܂��B�܂��͊ȈՓI�Ɏ������Ċm�F���ł��܂����� DSD DAC ��̎�����l���Ă݂܂��傤�B

DSD �����̍쐬

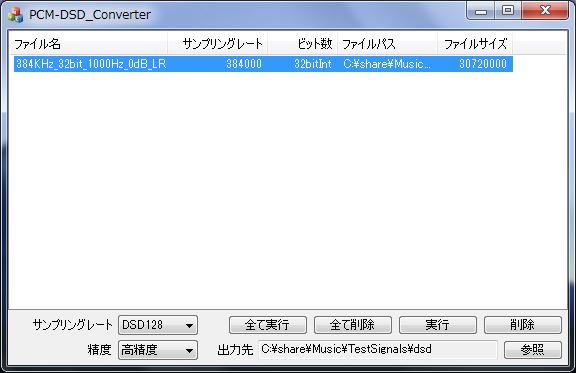

DSD �����̓_�E�����[�h�T�C�g������肷�邱�Ƃ��ł��܂��������p�ɂ̓e�X�g�M��������ƕ֗��ł��B�����ł܂��� DSD �t�H�[�}�b�g�̃e�X�g�M�����쐬���܂��B���Ƃ���32bit/384kHz 1KHz �� PCM �t�H�[�}�b�g�̐����g�M���� PCM-DSD_Converter ���g���� DSD �t�H�[�}�b�g�ɕϊ����܂��B�C���X�g�[������ PCM-DSD_Conberter.exe ���_�u���N���b�N���ĊJ�����E�B���h�E�ɕϊ����� WAVE �t�@�C�����h���b�O�A���h�h���b�v����ƃE�C���h�E���Ƀ��X�g�\�������̂ŕϊ�����t�@�C����I�����܂��B

DSD �̃T���v�����O���[�g��ݒ肵�܂�������� DSD128 �Ƃ��ĕϊ������s���Ă��܂��B�o�͂��ꂽ�t�@�C���� 384KH_32bit_1000Hz_0dB_LR_DSD128.dff �̂悤�Ɍ��t�@�C����_DSD+�T���v�����O���[�g.dff �ƂȂ�܂��B

DSD ����m�F

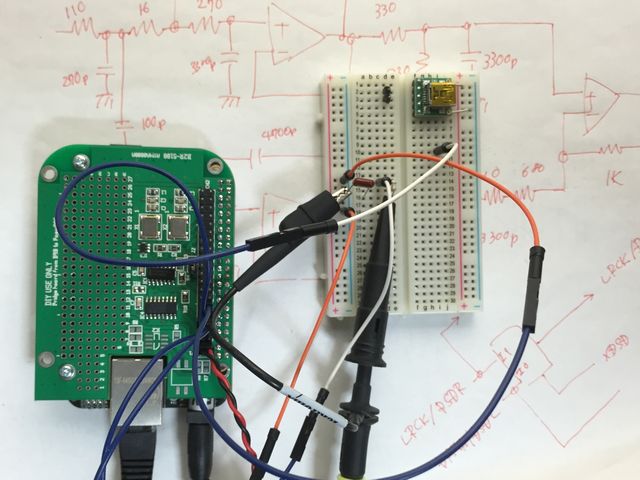

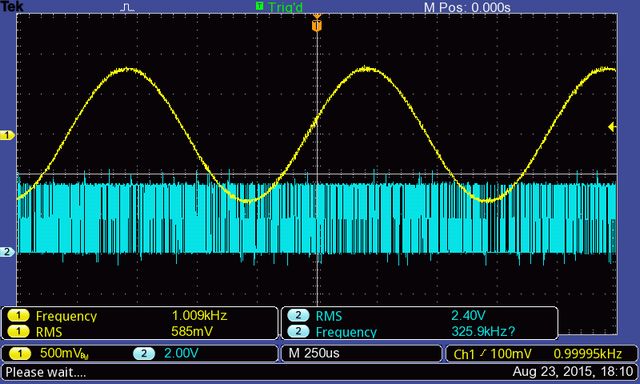

DSD �͌����I�ɂ̓p���X���x�ϒ��Ȃ̂ŕ�������ɂ̓��[�p�X�t�B���^��ʂ��Ηǂ��͂��ł��B�ł��̂� DSD �̓���m�F������ɂ� BeagleBone Black ����o�͂����f�[�^�X�g���[���� RC �t�B���^��ڑ����Ă��̏o�͂��I�V���X�R�[�v�Ŋώ@���܂��B�m�F����̂ɍĐ�����M���� 1kHz �Ȃ̂ŎՒf���g����10kHz ���x�� RC �t�B���^��ڑ����܂����B�{���ł���A�i���O�t�B���^�͎g�p���� DA �R���o�[�^�[�ɂ���ĎՒf���g���⎟�������肷�邱�ƂɂȂ�܂����A�����ł͊ȈՓI�Ȋm�F�����܂��B�ȉ��̂悤��BBB �u���b�W�����u���b�h�{�[�h�� LRCK/DSDR �M���������o����R�ƃR���f���T�őg���[�p�X�t�B���^�ɐڑ����Ă��܂��B

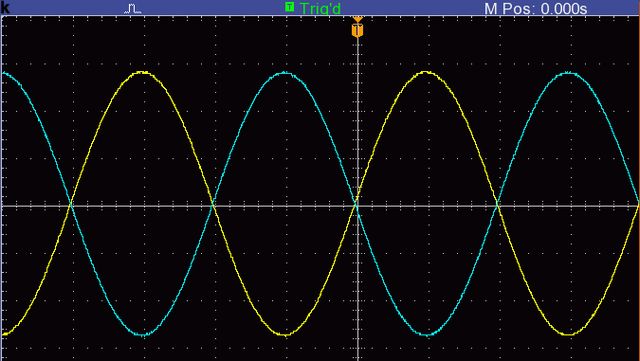

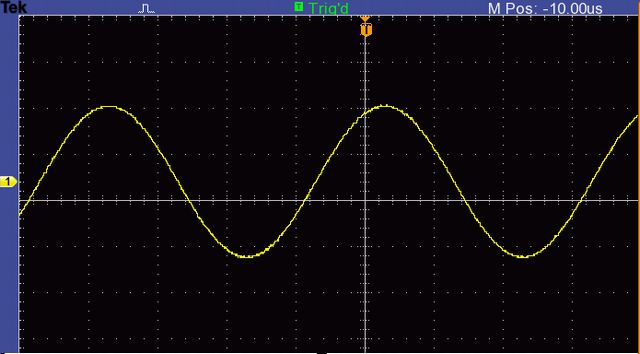

DSD �t�@�C���̍Đ��ɂ̓^�[�~�i���ł� play �R�}���h�͎g���Ȃ��̂� ympd �� GMPC �Ȃǂ� MPD �N���C�A���g����s���܂��B�I�V���X�R�[�v�ł̊ϑ����ʂ��ȉ��ɂȂ�܂��B���݂ɃI�V���X�R�[�v�ł� 20MHz �̑ш搧�����I���ɂ��Ă��܂��B

CH1 �� RC �t�B���^�̏o�͂� CH2 �� RC �t�B���^�ɓ��͂��� LRCK/DSDR �M���� �E�`���l���� DSD �f�[�^���̂��̂ł��B���ALRCK/DSDR �M���Ƃ͍Đ�����t�@�C���� PCM �t�H�[�}�b�g�f�[�^�̎��� LRCK (L �`���l���� R �`���l�����ʗp�N���b�N�M��)�ƂȂ� DSD �t�H�[�}�b�g�f�[�^�̎��� DSDR (DSD �� R �`���l���f�[�^�M��)�ƂȂ��Ď����I�ɐ�ւ��܂��B1kHz �̐����g�M������������Ă���̂��킩��܂��B

�ȏ�̂悤�� BeagleBone Black + Botic + BBB �u���b�W��� DSD �l�C�e�B�u�Đ��̊m�F�͂ł��܂����B���́A����ς� DSD �l�C�e�B�u�̉����Ă݂����Ȃ�܂��ˁB�Ƃ������Ƃł܂��܂��Â��E�E�E�B

DSD �Ή� DAC ��Ńl�C�e�B�u�Đ�

�ꌎ�قǑO�ɔ[�i����Ă��� DSD �Ή� DAC ��̎���i�̉Γ�����s���܂����B���삵����� DAC �`�b�v�� Cirrus Logic�i�� Wolfson�j�� WM8741 ���̗p���܂����B���̃`�b�v�͑啪�Â����\�I�ɂ��ŐV�̃f�o�C�X�ɔ�ח����e�Ȃ̂ŁA���X�Ƃ������͂���܂����A�n�[�h�E�F�A���[�h�� PCM �� DSD �̐�ւ����ł���̂Ŕ�r�I�ȒP�ɉ��������ł���̂Ɖ����I�ɂ��]�����ǂ��̂ō̗p���܂����B�������A�Â��`�b�v�̊��ɂ́i�Â�����H�j���i�P���������̂����_�ł��B

�v��̒��ӓ_

��H��v����ɓ����� BBB �u���b�W��iB2R-5100�j�� WM8741 �Ɛڑ�����ɂ͑����̉�H�̒lj����K�v�ɂȂ�܂��B

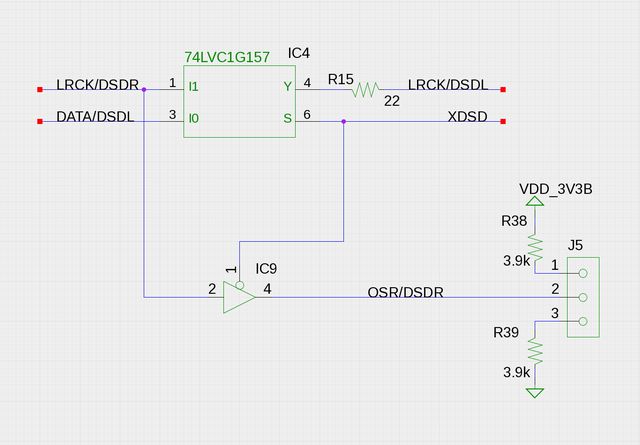

PCM/DSD �̐�ւ��M���iXDSD�j�� "H" �� PCM�A"L"�� DSD �ƂȂ��Ă��܂��� WM8741 �ł͂��̋t�ɂȂ��Ă��܂��iBBB �u���b�W����t�H�j�̂Ŕ��]��H���K�v�ɂȂ�܂��BBBB �u���b�W��̏o�͂ł� LRCK/DSDR�ADATA/DSDL �ƂȂ��Ă��܂��� WM8741 �ł� LRCK/DSDL�AOSR/DSDR�@�ɕϊ�����K�v������܂��BOSR/DSDR �� PCM ���[�h���̓I�[�o�[�T���v�����O���[�g�̐�ւ��M���ƂȂ� "H"�A"L" ������ �hHi-Z" �̏�Ԃ����K�v������܂��B������ DSD ���[�h���ɂ� R �`���l���̃f�[�^�X�g���[���ɂȂ�܂��B�����������邽�߂ɉ�H��lj����܂����B

PCM ���[�h�ł̓���ɂ̓}�X�^�[�N���b�N�iMCLK�j���K�v�ł��B�}�X�^�[�N���b�N�� BBB �u���b�W����� SCK �M���Ƃ��� 22.5792MHz �� 24.576MHz ����������܂��BWM8741 �̓}�X�^�[�N���b�N�������I�Ɍ��m���ăT���v�����O���[�g���ւ���̂ł��̂܂� MCLK �[�q�ɓ��͂��܂��B

����m�F

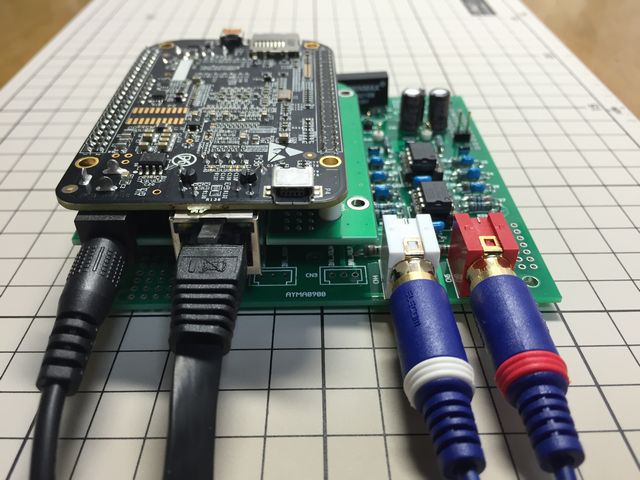

BeagleBone Black �Ɛڑ����ē�����m�F���܂��B�{���� BBB �u���b�W��̃s���w�b�_�[�� DAC ��̃s���\�P�b�g�ڐڑ�����̂ł����m�F�̂��߃I�X-���X�̃W�����p�[���C���[�Őڑ����Ă��܂��B�ڑ�����M���� BCK/DSD64�ADATA/DSDL�ALRCK/DSDR�ASCK�AXDSD����� SYS_5V�AVDD_3V3B�AGND �ł��B

�܂��� PCM ���[�h�ł̊m�F�ł��B

�m�F�� 192kHz/24bit 0dB 1kHz �̐M���ōs���܂����BWM8741 �̓T���v�����O���g���ɉ����� OSR/DSDR �[�q���ւ���K�v������܂��B�����܂������C�ɂ��ĂȂ������̂ŏo�͂����ꂸ�ł�܂����B�f�[�^�V�[�g�ǂ������炿���Ə����Ă���܂����B

"For optimum operation of the digital filtering and other processing on the WM8741 in PCM hardware mode, the user must ensure the correct value of OSR is set at all times. "

�Ƃ������Ƃ̓T���v�����O���g���ɂ���Đ�ւ����K�v�ɂȂ�̂Ŏ����I�ɐ؊�����ɂ͂���p�̉�H���K�v�ɂȂ�܂��B���̉�H�͌�قǍl���邱�Ƃɂ��ăX�C�b�`�ȂǂŎ蓮�Ő�ւ��邱�ƂɂȂ�܂��BOSR/DSDR �[�q�̓W�����p�[�iJ5�j�Ő�ւ��\�ɂ��Ă��܂��̂� "H" �iJ5 �� 1�ԃs����2�ԃs�����V���[�g�j�ɂ��Ĕg�`���ł�̂��m�F���܂����B

�ȁA�Ȃ�ƍ��`���l���ƉE�`���l���̈ʑ����t�ɂȂ��Ă��܂����B

�܂��� mono ���[�h�œ��삳���Ă���̂ł͂Ɗm�F���܂����� normal ���[�h�̐ݒ�ɂȂ��Ă��܂��B�v������H�}���������ƉE�`���l���� DAC �o�͂̐ڑ��𐳕��t�ɂ��Ă��܂����B�lj��H���K�v�ɂȂ�܂��� orz

�C����蒼���āA���� DSD ���[�h�ł��B

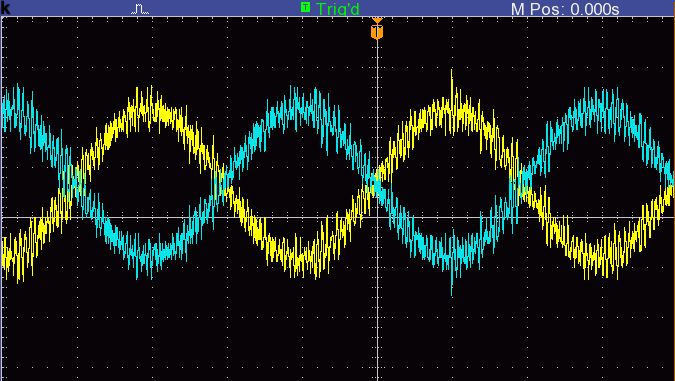

������삵���ړI�͂��� DSD ���[�h�ł̓�����m�F����ׂȂ̂ł�����Əڂ������Ă����܂��B�m�F�� 192kHz/24bit 0dB �� PCM �M����O�q�� PCM-DSD_Converter �� DSD64 �ɕϊ������M�����e�X�g�M���Ƃ��܂��B�ȉ��� WM8741 �̏o�́i�����A�t���j�ł��BDSD �M�����̂������Ă��釙���ϒ����L�̃m�C�Y������Ă���̂��킩��܂��B

LPF ��ʉ߂������t���̐M��������������H�Ō��Z������̔g�`���ȉ��ɂȂ�܂��BSCAD �t�H�[�}�b�g�u�b�N�ł́ASCAD �Đ����̃t�B���^�����Ƃ��āA�J�b�g�I�t 50kHz �ȉ��̃X���[�v -30dB/oct �ȏ�̃t�B���^����������Ă��܂����A�f�t�H���g�Őv�����t�B���^������ WM8741 �̃f�[�^�V�[�g�ɋL�ڂ���Ă���t�B���^�̒萔���g�p���Ă��܂��B���̃t�B���^�����̓J�b�g�I�t 100kHz �ƂȂ��Ă��� PCM �ɍœK�����������ƂȂ��Ă��܂��̂Ŗw�ǃm�C�Y�̌����͊m�F�ł��܂���BPCM �̍Đ��ł͖�肠��܂��� DSD �̍Đ��ɂ͖�肪����܂��ˁB

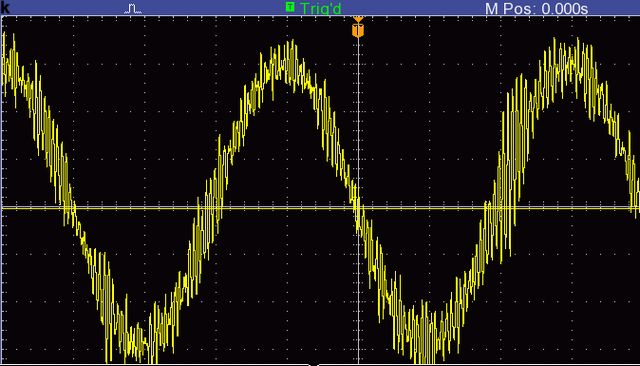

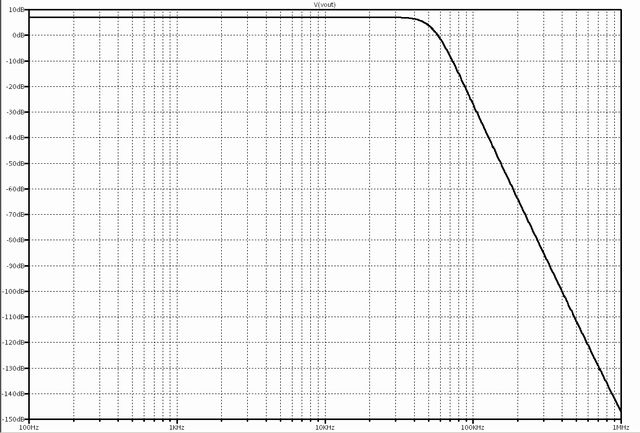

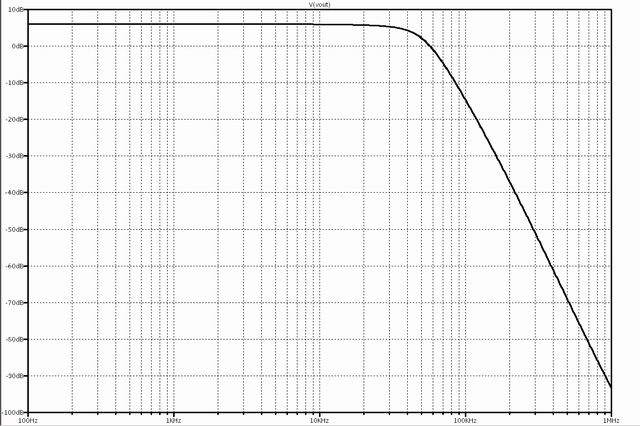

�����ŊO���̃u���b�h�{�[�h�ɃJ�b�g�I�t 50kHz �ȉ��̃X���[�v -30dB/oct �ȏ�̃t�B���^��g��ł݂܂����B���̃t�B���^��ʉ߂�����̔g�`���ȉ��ɂȂ�܂��B

�ǂ�����Ƃ܂����S�ɂ͏�������Ă��܂����p���肪�Ȃ��Ǝv���܂��B

���APCM ���[�h�ł͏o�͓d���͖� 2Vrms �ł��� DSD ���[�h�ł͖� 0.95Vrms �ɂȂ�܂��̂Ń��[�h���ւ��čĐ�����ɂ͒��ӂ��K�v�ł��B

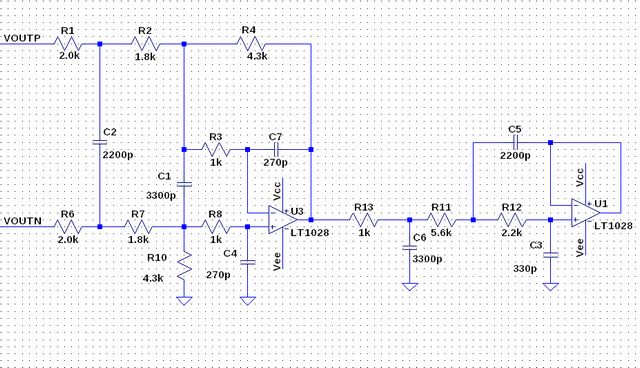

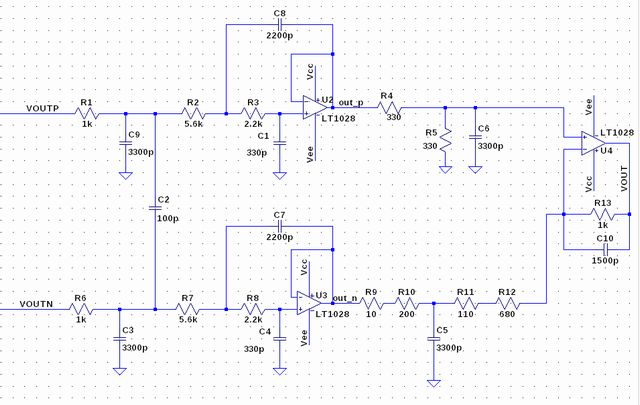

�u���b�h�{�[�h�ɑg�t�B���^�͈ȉ��̉�H�ł��B

LTspice �ŃV�~�����[�V���������t�B���^�����ł��BSCAD �t�H�[�}�b�g�Ő�������Ă�����������Ă���̂��m�F�ł��܂��B

�u���b�h�{�[�h�ɑg��H�� WM8741 �̃f�[�^�V�[�g�̐�����H�Ƃ͈قȂ��Ă��܂��̂ŁA������ۂɊ�̃��C�A�E�g������������H�̒萔��ύX���� SCAD �t�H�[�}�b�g�u�b�N�Ő�������Ă���t�B���^�����ɋ߂Â��Ă��܂��B�ȉ����̉�H�}�ł��B

LTspice �ŃV�~�����[�V�����������ʂł��B

mpd.conf �̕ύX

BBB + Botic �� DSD �l�C�e�B�u�Đ�����ƃt�@�C���ɂ���Ă͋Ȃ̍Ō�ōĐ�����~���A���̍� mpd �� CPU �g�p���� 95% �ȏ�ɂȂ錻�ۂ��������܂��B������������ɂ� /etc/mpd.conf �� audio_output �ɂ��� dsd_native_type ���f�t�H���g�ł� "3" �ƂȂ��Ă���Ƃ��� "0" �ɂ��܂��B

����� muraji ���ABBB �u���b�W��� Mi-take ������ DAC�iPCM1795�j�ł̑g�ݍ��킹�� DSD �l�C�e�B�u�Đ������݂Ă����Ƃ��ɔ����������ۂƂ��Ă��A�����������A�����������Ƃʼn������܂����B���낢��Ǝ����Ă��������� muraji ����Ɋ��ӂł��B

������

WM8741 ��͊��� 40�s���̃s���\�P�b�g�� BBB �u���b�W��̃s���w�b�_�[�ڐڑ����܂��B

���Ċ̐S�̉��ł����APCM ���[�h�ł� 192kHz/24bit �̉����� BBB �� RBD-02+ HG �L�b�g�ł̉��Ƃ̔�r�����܂����BRBD-02+ HG �L�b�g�ł��\���ɖ����ł��鉹���ł��i�ƕM�҂͎v���Ă��܂��j���AWM8741 DAC ��ł͂���ɏd�����������A����ł��ĉ��s�����L��������ۂł��BDSD �ɂ��Ă͏d�����Ƃ������͂��N���A�ɂȂ蓧�����������܂����B

DSD DAC ��Ƃ��Ď��삵���̂ł��� PCM ���[�h�̉����Ȃ��Ȃ��̂��̂ł��B����A�I�y�A���v���R�E�R���f���T�����낢��ύX���Ď������Ă݂����Ǝv���܂��B